�����������Ϊ�ִ���Ϣ������ҵ��ǿ�����棬һֱ���������ƶ��ż������ͨ�š����ֺͿ�ѧ����Ĵ��ºͷ�չ����20������Ҷ��������������ܲ����ݽ���������ľ���ܵ����Ľ���������뵼�峡ЧӦ����ܣ�MOSFET���������ܺ���Ҳ����������Ȼ�������������ߴ�IJ�����С����������������༼����ս�����ƣ�Ϊ��ͻ����Щ���ƣ����DZ���Ӹ���������˼������ܵ�δ����

�������ڴˣ�����������������ʥ�Ű�����У��Kaustav Banerjee�����쵼���о��Ŷ���Nature����The future transistorsΪ�ⷢ��չ����Perspective�����£��ܽ��˾���ܵķ�չ���̣������˾���ܵĹ������ƣ�������չ����δ������ܵķ�չ����

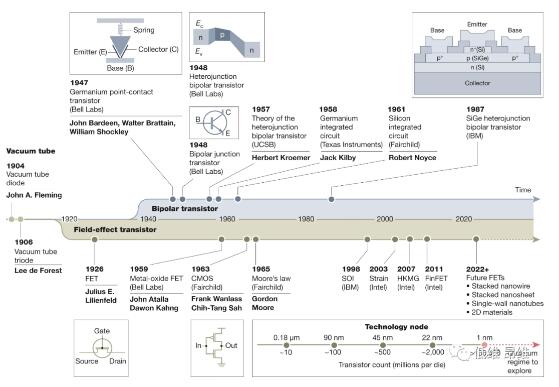

����ͼ1. ����ܵķ�չ��ʷ��

����ͼԴ��Nature 620, 501�C515 (2023).

�����������Ϊ�ִ���Ϣ�����Ļ�ʯ���䷢չ��ʷ���������ۺ�������Ŀ��ͻ�ơ���20������Ҷ����������ܵ��ݱ������ĸ�����ĸ߶ȼ��ɻ�����֤�����ഴ�ºͿƼ�������׳�����̡�

��������ܵķ�չ��ʷ�����ݵ�1947�꣬��ʱ����ʵ���ҵ���λ��ѧ�ҰͶ���John Bardeen������������Walter Brattain����Ф������William Shockley�������ɹ��ط����˵�һ̨��̬�����ܣ���Ҳ����Ϊ�ǵ�һ������ܡ������ͻ������չܵľ����ԣ������˰뵼��������ʱ��������֮��Ф��������1956������ŵ��������ѧ�����Ա������뵼�����۵Ĺ��ס�

����20����50�����60���������ܼ���ȡ���˷��ٵķ�չ����һ������ܹ㷺Ӧ���ڼ������ͨ���豸�У���������Ӵ���Ч���ߣ������˵����豸�Ľ�һ����չ�����ż��ɵ�·�����𣬾���ܵijߴ翪ʼ��С���Ӷ�ʹ�����豸���ӽ��պ�Ч��

����1971�꣬Ӣ�ض���˾�Ĵ�ʼ��֮һ��ǡ�Ħ������ˡ�Ħ�����ɡ���Ԥ��ÿ��Լ18��24���£����ɵ�·�ϵľ����������������ͬʱоƬ�ijɱ������롣��һ�����ƶ��˾���ܼ����ij�����չ��Ҳ�������ִ���Ϣ���������չ��

����ʱ������ƣ�����ܳߴ粻����С�����ɶȲ�����ߡ�20����80���������CMOS����������������뵼�壩���������룬���������Ĺ��Ĵ�����ͣ����ܵõ�����������20����90���������ܵ�ϸ�������칤�յIJ��ϸĽ���ʹ�ø��˵��ԡ��ƶ��绰���豸�����ܼ���������ͬʱ�۸����ͣ����ڻ�����Ϣ����ʱ���ɴ˿�����

����Ϊ�˷�������ܵ�δ������Ҫ�ȴӻ����������Ͳ���ԭ����ʼ���˽ⳡЧӦ����ܣ�FET���Ĺ�����ʽ�Լ������ִ������е���Ҫ�ԡ�FET��һ�ְ뵼��������������ǻ��ڵ糡���Ƶģ����Ѿ���Ϊ�ִ����ɵ�·�ĺ�����ɲ��֡�����FET�Ĺ���ԭ������չ�������δ���ķ�չ���йؼ����塣

������FET�У����������Ŀ���ͨ���ڰ뵼�������ʩ�ӵ糡��ʵ�֡������FET�����ǽ���-������-�뵼�峡ЧӦ����ܣ�MOSFET����MOSFET�Ľṹ�ɽ���-������-�뵼�幹�ɣ����н����缫�䵱�ż������������Ϊ��Ե�㣬�뵼��Ϊͨ����ͨ����MOSFET�еİ뵼���ǹ裬������������������衣

����MOSFET�Ļ���ԭ����ͨ������ͨ���еĵ���Ũ�������Ƶ����������������ż�ʩ�ӵ�ѹʱ���糡��Ӱ��뵼���еĵ��ӣ��Ӷ��������ӵ�Ũ�ȡ�����糡ЧӦ���°뵼��ͨ���ĵ絼�ʷ����仯���Ӷ����ƴ�Դ����©���ĵ���������ͨ���ı��ŵ�ѹ�Ĵ�С�ͼ��ԣ����ǿ���ʵ�ֵ����Ŀ��ؿ��ƣ��Ӷ�ʵ����Ϣ�Ĵ洢�ʹ�����

����ͼ2. ��ЧӦ����ܣ�FET����������ԭ���Ļ�����

����ͼԴ��Nature 620, 501�C515 (2023).

Ȼ��������MOSFET�ߴ�IJ�����С�������������һϵ���Ͼ�����ս����Щ��ս�������Գߴ�ЧӦ�ļӾ磬���漰���������ĸ������⡣

�������ȣ����ž���ܳߴ�ļ�С��һЩ����Ӱ���ø����������Ӷ������˾���ܵ����ܺ���Ч������֮һ��©��ЧӦ����Դ©������й©�������ųߴ��С��������ͨ���е������ܵ����ƣ��Ӷ�����©��ЧӦ�����ӡ��ⲻ��Ӱ���˾���ܵĿ����ٶȣ������ܵ��µ������ȶ����Ӷ�Ӱ���������Ŀɿ��Ժ�һ���ԡ�

������Σ���������͵��ݵ�����Ҳ�Ծ���ܵ����ܲ�����Ӱ�졣���ž���ܳߴ��С����֮�����ĵ缫��Դ©����ȵijߴ�Ҳ��֮��С�����¼����������ӡ���ʹ�õ����������еĴ����ø��Ӹ��ӣ������˾���ܵ���Ӧ�ٶȺ͵����������������⣬�������ݵ�����ҲӰ���˾���ܵĸ�Ƶ���ܣ������ź�˥�����������ӣ��Ӷ�Ӱ������Ϣ�Ĵ���������й©����������Ҳ�Ǿ�������ٵ���ս֮һ�����ž���ܳߴ����С��й©�����������е�ռ�������ӣ��Ӷ����¹��ĵ����ӡ�й©���������˷����������ᵼ�������ķ������⣬Ӱ����ɿ��Ժ�������

�������⣬����ܵ������ѶȺͳɱ�Ҳ�������ӣ���Լ�����һ���ķ�չ�����ųߴ����С��������̱�ø��Ӹ��ӣ���Ҫ���߾��ȵĹ��պ��豸��ͬʱ���µIJ��Ϻ������ṹ������Ҳ����������ĸ����ԡ��ⲻ������������ijɱ��������ܵ�����������еIJ��ȶ��Ժͱ����ԣ�Ӱ����������һ���ԺͿɿ��ԡ�

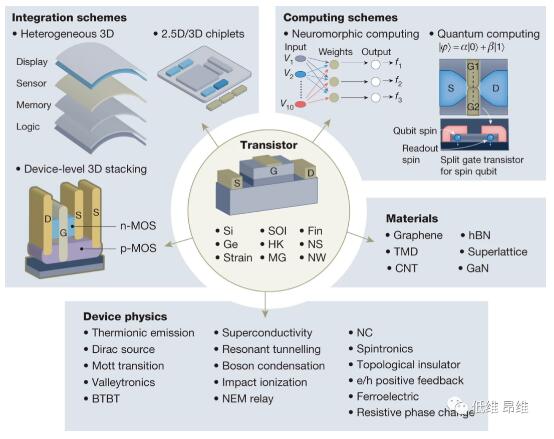

����ͼ3.�������������Ϣ������ҵ���������ǿ�����档 ����ͼԴ��Nature 620, 501�C515 (2023). ��������ܵ�δ����չ�������ƶ���Ϣ��������ķ�չ���������Ӱ�������ճ�����ķ������档

�������ȣ�һ������עĿ�ķ������µ������ṹ�Ͳ��ϵij��֣���ʵ�ָ��ߵ����ܺ���Ч�������ݳ�ЧӦ����ܣ�Negative Capacitance FET�����NC FET����һ�����о�DZ���ļ�����������������ϵĸ��������ԣ�����ͻ�ƴ�ͳ����ܵ�������ƣ�ʵ�ָ���Ч�ĵ�ɿ��ơ�ͨ����ͨ���������������籡Ĥ��NC FET����ʵ�ֱȴ�ͳMOSFET��С�Ĵ���ֵ�ڷ����Ӷ����������ܡ����⣬�����ų�ЧӦ����ܣ�Suspended Gate FET����Mott�������ſؾ���ܣ�Mott-G FET��ͨ�������µ������ṹ�������ϣ�ʵ���˸�С������ֵ�ڷ����ߵĵ����ܶȡ���Щ�����Ե������ṹ�Ͳ��Ͻ�Ϊ����ܵ�δ����չ�����µĿ����ԣ���������������ķ��ٽ�����

������Σ���ά���ɼ�������Ϊ�����δ����չ����Ҫ����ͳ�ϣ��������ƽ���ϲ��֣������ż����ķ�չ����ֱ�ѵ��ĸ�����������Ҫ��ͨ����ֱ�ѵ���������ʵ�ָ��ߵ����������ܶȣ������Լ��ٵ�·�����ij��ȣ��Ӷ������ĺ��ӳ١���ά���ɼ��������벻�������ṩ����ļ�����Դ��������Ϊ��Ϣ������������µĿ����ԡ����磬��ά�ѵ��Ĵ洢���ʹ�������Ԫ���Ը����ܵ����ӣ��Ӷ��������ݴ���ʹ������ƶ�����������ķ��ٷ�չ�����⣬��ά���ɼ���������Ϊ���������˹����ܺʹ����ݵ������ṩ��ǿ��ļ����������ƶ��Ƽ����µı߽硣

�����������Ϸ��棬����ܵ�δ�������漰���µļ��㷶ʽ�ͼ���������̬��������Ӽ�������ͼ��㷽��������ո¶ͷ�ǣ����ǽ����ı䴫ͳ������Ĺ�����ʽ�;����ԡ�����̬����ģ�������ԵĹ���ԭ����ͨ��ģ����Ԫ֮������Ӻ�����ã�ʵ�ָ�Ч��ģʽʶ���ѧϰ�����Ӽ�������������λ��Qubit���ĵ��Ӻ;������ԣ�ʵ�����ڴ�ͳ��������Խ���������ϵ�ͻ�ơ���Щ���ͼ��㷽���Ծ���ܵ����ܺ���Ч����˸��ߵ�Ҫ���ƶ��˾���ܼ����Ľ�һ����չ��ͨ���Ż�����ܵ���ƺͲ���ѡ����������Ϊ����̬��������Ӽ���������ṩ����ǿ���Ч�ļ���ƽ̨��

������������������ܵ�δ��������������ܵĻ�����ǰ����ͨ�����ϵĴ��ºͼ���ͻ�ƣ����ǿ����ڴ��������������ṹ���Ƚ����Ϻ���ά���ɼ��������룬�Լ����ͼ��㷶ʽ��ո¶ͷ�ǡ���Щ��չ�������ƶ���Ϣ��������ķ�չ������Ӱ�쵽ҽ�ơ�ͨ�š���Դ����ѧ���̵ȶ������δ����ѧ�Һ���ʦ�IJ��ϴ��½�Ϊ����ܵ�δ����չ�ṩ���ߵĶ���������Ϊ���ഴ��������õ�δ����

|